Author Affiliations

Abstract

1 Wuhan National Laboratory for Optoelectronics, Huazhong University of Science and Technology, Wuhan 430074, China

2 e-mail: hailongzhou@hust.edu.cn

Optical computing has shown immense application prospects in the post-Moore era. However, as a crucial component of logic computing, the digital multiplier can only be realized on a small scale in optics, restrained by the limited functionalities and inevitable loss of optical nonlinearity. In this paper, we propose a time-space multiplexed architecture to realize large-scale photonic-electronic digital multiplication. We experimentally demonstrate an -bit photonic-electronic digital multiplier, and the multiplication with a 32-bit number is further executed at 25 Mbit/s to demonstrate its extensibility and functionality. Moreover, the proposed architecture has the potential for on-chip implementation, and a feasible integration scheme is provided. We believe the time-space multiplexed photonic-electronic digital multiplier will open up a promising avenue for large-scale photonic digital computing.

Photonics Research

2024, 12(3): 499

Author Affiliations

Abstract

1 Wuhan National Laboratory for Optoelectronics, Huazhong University of Science and Technology, Wuhan 430074, China

2 Optics Valley Laboratory, Wuhan 430074, China

With the advancement of deep learning and neural networks, the computational demands for applications in wearable devices have grown exponentially. However, wearable devices also have strict requirements for long battery life, low power consumption, and compact size. In this work, we propose a scalable optoelectronic computing system based on an integrated optical convolution acceleration core. This system enables high-precision computation at the speed of light, achieving 7-bit accuracy while maintaining extremely low power consumption. It also demonstrates peak throughput of 3.2 TOPS (tera operations per second) in parallel processing. We have successfully demonstrated image convolution and the typical application of an interactive first-person perspective gesture recognition application based on depth information. The system achieves a comparable recognition accuracy to traditional electronic computation in all blind tests.

optoelectronic compute wearable devices micro-ring resonator hand gesture recognition Opto-Electronic Science

2023, 2(12): 230017

Author Affiliations

Abstract

1 Wuhan National Laboratory for Optoelectronics, Huazhong University of Science and Technology, Wuhan 430074, China

2 Optics Valley Laboratory, Wuhan 430074, China

3 Galileo Advanced Technology Lab, Huawei Technologies, Shenzhen 518129, China

4 Institute of Strategic Research, Huawei Technologies, Shenzhen 518129, China

5 e-mail: xuwenwei@huawei.com

6 e-mail: jjdong@mail.hust.edu.cn

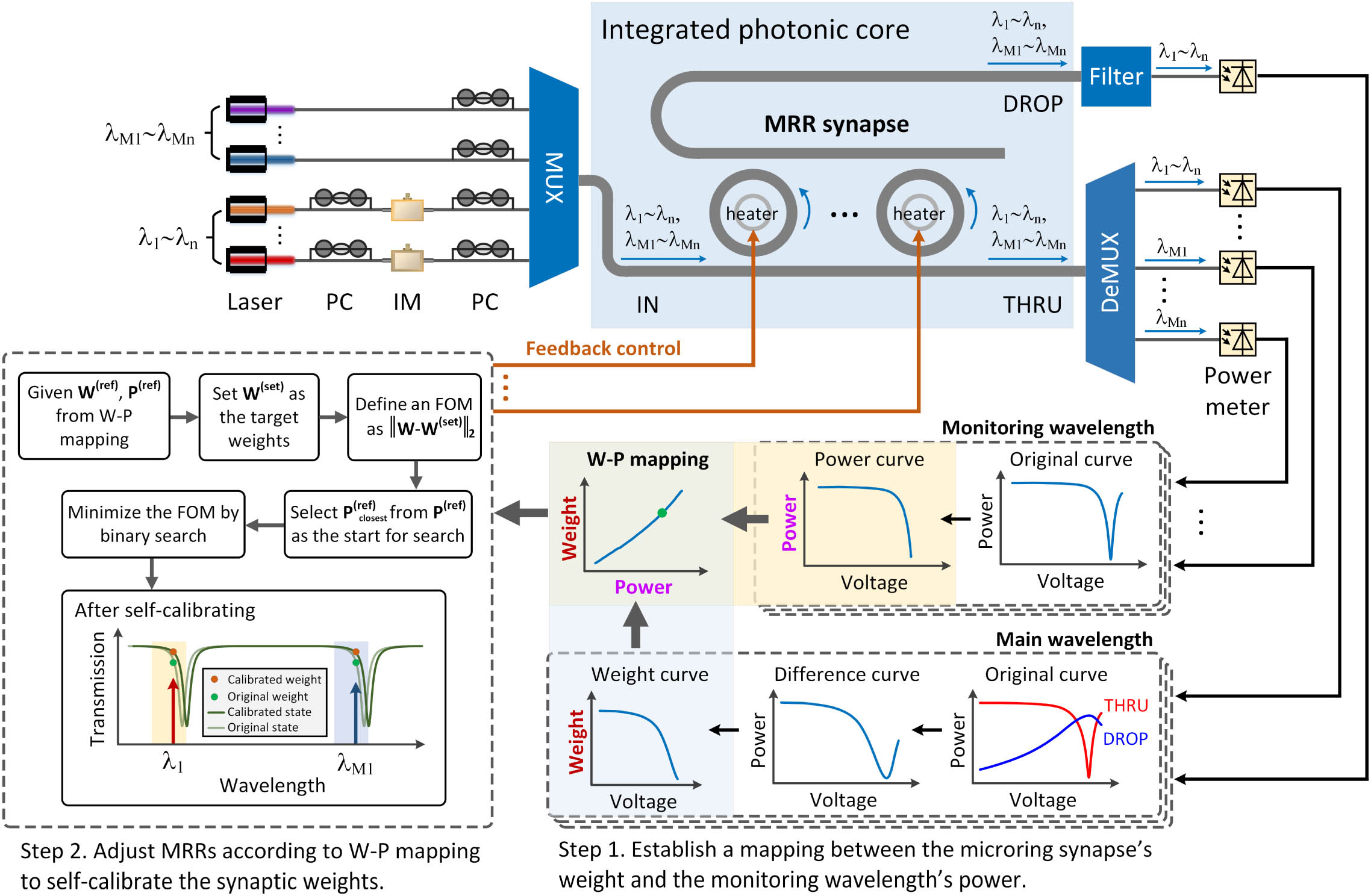

corresponding author guidelines for details."?>As a resonator-based optical hardware in analog optical computing, a microring synapse can be straightforwardly configured to simulate the connection weights between neurons, but it faces challenges in precision and stability due to cross talk and environmental perturbations. Here, we propose and demonstrate a self-calibration scheme with dual-wavelength synchronization to monitor and calibrate the synaptic weights without interrupting the computation tasks. We design and fabricate an integrated microring synapse and deploy our self-calibration scheme to validate its effectiveness. The precision and robustness are evaluated in the experiments with favorable performance, achieving 2-bit precision improvement and excellent robustness to environmental temperature fluctuations (the weights can be corrected within 1 s after temperature changes 0.5°C). Moreover, we demonstrate matrix inversion tasks based on Newton iterations beyond 7-bit precision using this microring synapse. Our scheme provides an accurate and real-time weight calibration independently parallel from computations and opens up new perspectives for precision boost solutions to large-scale analog optical computing.

Photonics Research

2023, 11(2): 347

1 华中科技大学武汉光电国家研究中心,湖北 武汉 430074

2 湖北光谷实验室,湖北 武汉 430074

随着人工智能技术的高速发展,全球的计算量急剧增长,需要以快速、高效的方式处理海量数据,这对计算硬件的算力和能效提出了较高的要求。受限于电子器件的固有极限和冯·诺依曼架构,传统的电子计算在速度和能效方面遇到了难以突破的瓶颈。光电智能计算充分融合光学的多维复用、大带宽、低能耗等优势和电学的细粒度灵活控制特性,具有光算电控和软硬协同的特点,是一种更实用、更有竞争力的人工智能计算加速方案。回顾了光电智能计算的研究进展,探讨了目前用于光学信号处理和光学神经网络的主流计算架构在线训练算法以及算力、能效提升方面的挑战,并进行了展望。

光计算 光电智能计算 人工智能 计算加速 光学信号处理 光学神经网络 中国激光

2022, 49(12): 1219001